18EC33

(06 Marks)

d Semester B.E./B.Tech. Degree Examination, June/July 2025 **Electronics Devices**

Time: 3 hrs. Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

# Module-1

- a. Explain different types of bonding forces in solids.

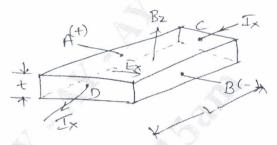

- b. Consider a semiconductor bar with w = 0.1 mm,  $t = 10 \mu m$  and L = 5 mm for  $B_z = 10 kg$  in the direction shown in Fig.Q1(b) and a current of 1 mA.  $V_{AB} = -2mV$ , and  $V_{CD} = 100mV$ . Find the type of semi-conductor carriers and mobility of the majority carriers. Given  $1 \text{ kg} = 10^{-5} \text{ wb/cm}^2$ .

Fig.Q1(b)

(06 Marks)

What are intrinsic and extrinsic materials? Explain briefly by taking suitable example. (08 Marks)

- Explain classification of semiconductor, insulator and metals using energy band diagram.

- b. A silicon is doped with 10<sup>17</sup> Arsenic atoms/cm<sup>3</sup>. What is the equilibrium hole concentration P<sub>0</sub> at 300°K? Sketch the resulting band diagram showing where is E<sub>F</sub> relative to E<sub>i</sub>. Assume  $n_{i}^{2} = 2.25 \times 10^{20}$ .

- c. Derive an expression for conductivity and mobility from random thermal motion or electron in solid. (08 Marks)

Module-2

Describe the structure and operation of solar cell. Indicate the significance of fill factor. 3

b. With a neat diagram, describe in detail avalanche breakdown and derive an approximate analysis of avalanche multiplication. (10 Marks)

OR

- Discuss the reverse bias p-n junction indicating the minority carrier distribution and variation of quasifermi levels. (10 Marks)

- b. Derive an expression for current and voltage for an illuminated junction of photodiode and discuss the operation in various quadrants in I-V characteristic. (10 Marks)

## Module-3

- a. Describe the effect of excess hole distribution in cutoff and saturation regime with neat 5 (10 Marks)

- b. Explain the switching effect in a common-emitter transistor circuit and specification for switching transistor with neat diagram. (10 Marks)

## OR

- Describe the schematic representation of p-n-p transistor and summarize the hole and electron flow with proper biasing. (10 Marks)

- b. Derive the Ebers-Moll equations and represent the coupled-diode equivalent circuit.

(10 Marks)

# Module-4

- a. Explain the ideal capacitance voltage characteristics of an MOS capacitor with p-type substrate. (06 Marks)

- b. Illustrate the structure and operation of pn-JFET by varying V<sub>GS</sub> and V<sub>DS</sub> independently.

c. List the different types of MOS structures and its symbols.

(06 Marks)

#### OR

- Explain the operation of MOS capacitor using energy band diagram for p-type substrate when:

- Negative gate bias

- ii) Moderate positive gate bias

- iii) Large positive gate bias.

(08 Marks) (06 Marks)

- b. Distinguish between JFET and MOSFET.

- c. Describe small signal equivalent circuit of a n-channel pn JFET, with suitable diagram.

(06 Marks)

- a. List out the different types of IC's along with the advantages and disadvantages and applications of IC's.

- b. Describe with neat schematic diagram, Rapid Thermal Processor (RTP) and typical timetemperature profile. (10 Marks)

#### OR

a. Explain the fabrication of CMOS twin well process.

(10 Marks)

b. Describe with neat schematic diagram, optical stepper.

(10 Marks)