21EE42

Max. Marks: 100

ALO Note: Answer any FIVE full questions, choosing ONE full question from each module.

- 15, 16, 18) + d(24, 25, 26, 27, 28, 29, 30, 31) using Karnaugh map method.

- Design a combinational logic circuit to output the 2's complement of a 4-but binary number

- Simplify each output function using K-map and write reduced equations and draw the (12 Marks)

## OR

- Find a minimal sum for the following Boolean function using Quine Mc Cluskey method 2 and prime implicant table reduction  $f(a, b, c, d) = \Sigma(3, 4, 5, 7, 10, 12, 14, 15) + \phi(2)$ .

- Obtain the minimal sum using K-map for the following function  $f(a, b, c, d) = \sum m(1, 2, 3, 5, 6, 7, 11, 12, 13, 14, 15)$ . Find all the prime implicants and essential prime implicants. Draw the logic diagram.

# Module-2

Implement full subtractor using a decoder and write the truth table. 3

(06 Marks)

(12 Marks)

Design even parity generator circuit for 4 bit I/P using multiplexer. b.

(08 Marks)

Write a note on 4-bit priority encoder. c.

(06 Marks)

Design a 2-bit comparator using gates. a.

(10 Marks)

- Explain how a full subtractor can be realized using two half subtractor and OR-Gate.

- (10 Marks)

- Draw the logic symbol of the edge triggered JK flip-flop. Obtain its characteristics equations and draw the timing diagram. (08 Marks)

- b. Explain different types of triggering mechanism employed in flip-flops. (06 Marks)

- Draw the logic circuit of D latch using only NAND gates and explain its operation.

(06 Marks)

- Explain how T-flip-flop can be converted into SR flipflop. 6 a. (07 Marks)

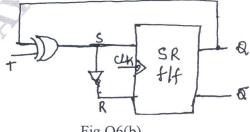

- Write the truth table for the following circuit and show that it acts as a T-flip-flop.

Fig Q6(b)

1 of 2

(07 Marks)

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

ii) Combinational and c. Distinguish between i) Synchronous and Asynchronous circuits (06 Marks) sequential circuits.

Module-4

- Design a synchronous counter with sequence 0, 1, 3, 7, 6, 4, 0 using JK flip flop. (08 Marks)

- Design a 4-bit binary ripple up counter using negative edge triggered JK f/f. (04 Marks) b. (08 Marks)

- List the steps involved in the design of asynchronous counter.

Draw a 4 bit Johnson counter, its truth table and timing diagram. Explain its operation. a. (08 Marks)

(08 Marks)

Explain the operation of 4-bit bidirectional shift register. **b**.

List the applications of shift registers. C.

(04 Marks)

Module-5

- Distinguish between Mealy and Moore model with necessary block diagram. (08 Marks) 9

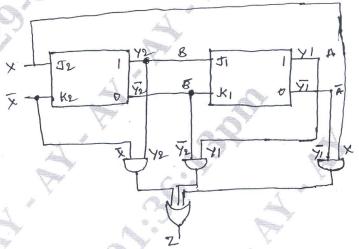

- Analyze the synchronous circuit of the figure shown Q9(b) i) Write the excitation and output function ii) Form the excitation and state tables.

Fig Q9(b)

(12 Marks)

**OR**

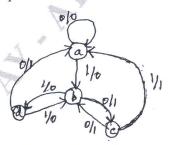

Obtain the transition table for the state diagram shown below Fig Q10(a) and design a sequential circuit using JK flip-flop.

Fig Q10(a) State diagram

(08 Marks)

Explain the classification of semiconductor memories.

(04 Marks)

Discuss the following types of ROM memory i) EPROM iii) PROM iii) EEPROM.

(08 Marks)