|     | 30.5 () |    |        |

|-----|---------|----|--------|

| USN |         | 0. | 17EC33 |

# Third Semester B.E. Degree Examination, Dec.2023/Jan.2024 Analog Electronics

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

# Module-1

- a. For a common Emitter with voltage divider bias, derive the expression fro voltage gain, input impedance and output impedance sign re model. (10 Marks)

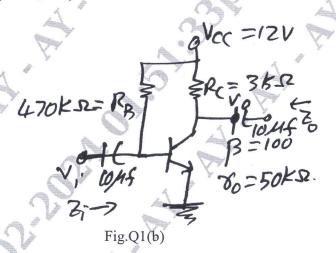

- b. For the networks shown in Fig.Q1(b).

- i) Determine

- ii) Find  $Z_i(\text{with } r_0 = \infty)$

- iii) Calculate  $Z_0(\text{with } r_0 = \infty)$

- iv) Determine  $A_V(\text{with } r_0 = \infty)$

(10 Marks)

# OR

a. Draw the complete hybrid equivalent (h-parameters model) circuit of two part networks for BJT and obtain equation for voltage gain and current gain. (10 Marks)

Module-2

b. Draw circuit of Hybrid  $\pi$ -model of transistor and mention various parameters.

3 a. Explain construction and characteristics of n-channel JFET.

- (08 Marks)

- b. Explain transfer characteristics of FET and mention the required equation.

- (08 Marks)

(10 Marks)

- c. Mention differences between depletion type and enhancement type MOSFET.

- (04 Marks)

# OR

- a. Draw the circuit of common source voltage divider using JFET and derive the expression for Z<sub>i</sub>, Z<sub>0</sub> and A<sub>v</sub>. (10 Marks)

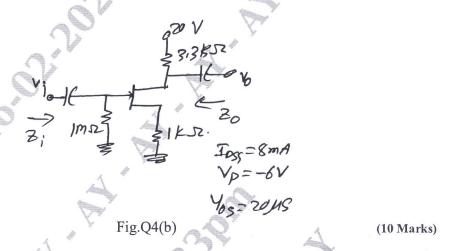

- b. The self-bias configuration has operating point at  $V_{GS} = -2.6V$ ,  $I_{Dn} = 2.6mA$ . The circuit is a shown in Fig.Q4(b).

Determine: i)  $g_m$  ii)  $r_d$  iii)  $Z_i$  iv)  $Z_0$  v)  $A_V$  without  $r_d$ .

## Module-3

- 5 a. Derive expression for lower cut-off frequency w.r.t C<sub>g</sub> and mention the effect of C<sub>C</sub> and C<sub>E</sub> frequency. (08 Marks)

- b. For FET amplifier circuit determine lower cut off frequency and sketch frequency response curve using the following parameters:

$$\begin{split} &C_Q=0.01\mu f,\quad C_C=0.5\mu f,\quad C_S=2\ \mu f,\quad R_{Sig}=10K\Omega,\\ &R_G=1m\Omega,\quad R_D=4.7K\Omega,\quad R_S=1\ K\Omega,\quad R_L=2.2K\Omega,\\ &I_{DSS}=8mA,\quad V_P=-4V,\quad r_d=\infty\Omega,\quad V_{DD}=20V. \end{split} \tag{12 Marks}$$

### OR

- 6 a. Draw high frequency ac equivalent circuit of FET amplifier and obtain higher cut off frequency for i/p and o/p. (12 Marks)

- b. With the help of suitable equations and neat diagram, explain the multistage frequency effect. (08 Marks)

# Module-4

- 7 a. Draw the block diagram of voltage series feedback amplifier and derive the expression for gain with feedback, i/p and o/p impedances. (10 Marks)

- b. Determine the voltage gain, i/p and o/p impedance with feedback for voltage series feedback having A = -100,  $R_i = 10 \text{K}\Omega$ ,  $R_0 = 20 \text{K}\Omega$ , for feedback factor of B = -0.1. (06 Marks)

- c. State the merits of -ve feed back in amplifier. (04 Marks)

## OR

- Draw the circuit of phase shift oscillator using JFET and explain its operation. Also mention the equation of for frequency of oscillations.

- b. Draw the circuit of Wien Bridge oscillator and derive the expression for frequency of oscillation. Also explain the circuit connection and working. (10 Marks)

- Module-5

Draw the circuit of series fed class-A amplifier and derive the expression for maximum 9 efficiency with operation.

- b. Define harmonic distortion and calculate the harmonic distortion components for an o/p signal having the fundamental amplitude of 2.5V, second harmonic amplitude of 0.25V, third harmonic of 0.1V and fourth harmonic amplitude of 0.05V, also find total harmonic distortion. (10 Marks)

- With the help of a block diagram, explain short voltage regulation and also explain how the 10 same can be implemented using BJT. (12 Marks)

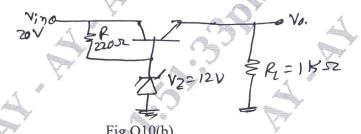

- b. Calculate the output voltage and the zener current in the regulator circuit. Refer Fig.Q10(b).

(08 Marks)