17EC33

# Third Semester B.E. Degree Examination, June/July 2023 **Analog Electronics**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

Derive an expression for  $A_V$ ,  $Z_i$ , and  $Z_0$  for CE –fixed bias using  $r_e$  equivalent model.

b. What is an emitter follower? Discuss about emitter follower circuit and find Zi, Z<sub>0</sub> and A<sub>v</sub> using r<sub>e</sub> – model. (10 Marks)

- 2 Define h-parameters and derive h-parameters model of CE – BJT. (10 Marks)

- b. For an emitter bias circuit (capacitor is unbypassed), determine re, Zi, Zo and Av. Given  $R_B = 470 \text{K}\Omega$ ,  $R_C = 2.2 \text{K}\Omega$ ,  $V_{CC} = 20 \text{V}$ ,  $R_E = 0.56 \text{K}\Omega$ ,  $C_E = 10 \mu\text{F}$ ,  $\beta = 120$ ,  $r_0 = 40 \text{K}\Omega$ ,  $C_C = 10 \mu F$ .

Module-2

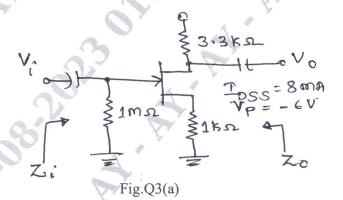

For the self-bias configuration shown has an operating point  $V_{GSQ} = -2.6V$  and  $I_{DQ} = 2.6mA$ with  $I_{DSS}=8mA$  and  $V_p=-6V$ . Assume  $Y_{OS}=20\mu S$ . (Refer Fig.Q3(a)). Find: i)  $g_m$  ii)  $r_d$  iii)  $Z_i$  iv)  $Z_0$  v)  $A_V$ .

(10 Marks)

Derive an expression for Zi, Zo and Av for JFET source follower circuit using small signal model. (10 Marks)

OR

- Explain the small-signal model of the FET. (10 Marks)

- Write the ac equivalent circuit for voltage divider JET configuration. Determine Z<sub>i</sub>, Z<sub>0</sub> and (10 Marks) Av.

### Module-3

- 5 a. Determine:

- i) The common logarithm of the number  $2.2 \times 10^3$

- ii) The power gain is decibles for  $P_0 = 100$ m walts,  $P_i = 5$ m watts

iii) Find voltage gain in dB for o/p voltage 100V and  $R_0 = 20\Omega$ . (08 Marks)

b. Prove that miller effect of input capacitance.  $C_{mi} = (1 - A_V) C_f$  and output capacitance

$$C_{m_0} = \left(1 - \frac{1}{A_v}\right) C_f. \tag{12 Marks}$$

#### OR

- 6 a. Derive an expression for high frequency response of FET amplifier. (12 Marks)

- b. Discuss the effect of various capacitors on multistage frequency response. (08 Marks)

### Module-4

- 7 a. Discuss about the different types of feedback connections indicating input and output signal.

(12 Marks)

- b. With a neat circuit diagram, explain the working principle of FET RC-phase-shift oscillator.

(08 Marks)

#### OR

- 8 a. What are the effects of negative feedback in an amplifier? Show how bandwidth of an amplifier increases with negative feedback. (10 Marks)

- b. A crystal has the following parameter L=0.334H,  $C_m=1pF$ , C=0.065pF and  $R=5.5K\Omega$ . Calculate the series resonant and parallel resonant frequency and Q of the crystal. (10 Marks)

### Module-5

- 9 a. With a neat circuit diagram explain the operation of a transformer coupled class A power amplifier. (10 Marks)

- b. For the following distortion values, calculate:

- i) THD

- ii) Fundamental power component

- iii)Pt.

Given:

$$D_2 = 0.2$$

,  $D_3 = 0.02$ ,  $D_4 = 0.06$ ,  $I_L = 3.3$ A and  $R_C = 4\Omega$ . (10 Marks)

#### OR

- 10 a. With a neat circuit diagram, explain the working principle of complementary symmetry push pull amplifier. (10 Marks)

- b. With a neat circuit diagram, explain the working principle of fold back current limiting circuit. (10 Marks)

\* \* \* \* \*