## CBCS SCHEME

15EE35 USN Third Semester B.E. Degree Examination, June/July 2023 MCA **Digital System Design** Library Time: 3 hrs Max. Marks: 80 Note: Answer any FIVE full questions, choosing ONE full question from each module. Module-1 1 Simplify the following function using Quine McClusky method:  $P = f(w, x, y, z) = \Sigma(7, 9, 12, 13, 14, 15) + \Sigma d(4, 11)$ (10 Marks) b. Write the truth table of the logic circuit having 4 inputs: A, B, C, D and an output Y.  $Y = f(A, B, C, D) = \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} \overline{C} \overline{D} + A \overline{D} \overline{C} \overline{D} + A \overline{$ Also simplify the Boolean expression and implement the logic circuit using NAND gates only. (06 Marks) Simplify the given function using MEV technique taking the least significant variable as the map entered variable.  $f(a, b, c, d, e) = \Sigma(1, 3, 4, 6, 9, 11, 12, 14, 17, 19, 20, 22, 25, 27, 28, 30) + \Sigma d(8, 10, 24, 26)$ (08 Marks) b. Simplify the following function using K-map technique and implement using basic gates:  $f(A, B, C, D) = \pi M(0, 2, 4, 10, 11, 14, 15)$ (08 Marks) Module-Distinguish between a decoder and an encoder implement full adder using IC74138. 3 (06 Marks) Write a short note on 4 bit parallel adder. (04 Marks) c. Implement the following Boolean function using 4:1 multiplexer:  $Y = f(A, B, C, D) = \Sigma m(0, 1, 2, 4, 6, 9, 12, 14)$ (06 Marks) OR Explain the working of carry look ahead adder with the help of block diagram. (06 Marks) Define multiplexer and demultiplexer. Draw the functional diagram. (05 Marks) c. Design priority encoder with three inputs, with middle bit at highest priority encoding to 10, most significant bit at next priority encoding to 11 and least significant bit at least priority encoding to 01. (05 Marks) Module-3 Explain the operation of master-slave JK flip flop with logic diagram, truth table, symbol 5 and timing diagram. (10 Marks) Obtain the characteristic equation of a SR flip flop. (06 Marks) OR Convert SR flipflop to a JK flipflop. 6 (06 Marks) Explain with the timing diagram the working of SR latch as a switch debouncer. (10 Marks)

ffinportant Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice.

Module-4

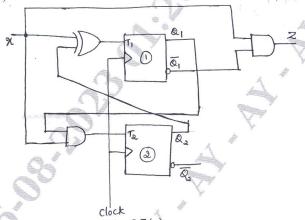

Construct the transition table, state table and state diagram for the Moore sequential circuit shown in the Fig.Q7(a).

Fig.Q7(a)

(10 Marks)

Explain Melay and Moore models of a clocked synchronous sequential circuit.

(06 Marks)

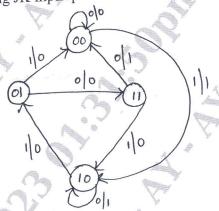

Design sequential circuit using JK flipflop. The state diagram shown in Fig.Q8(a). 8

Fig.Q8(a)

(12 Marks)

Define state, state equation, state diagram and state table.

(04 Marks)

Module-5

(10 Marks)

Explain various data types available in VHDL. Implement a single bit comparator for all input combinations in VHDL. b.

(06 Marks)

OR

Compare VHDL and Verilog. 10

(10 Marks)

Implement a 4:1 multiplexer using a process and case statement in VHDL.

(06 Marks)