| CO Same To | Man 4 / 1 / No                          |       |  |

|------------|-----------------------------------------|-------|--|

| 2.2.       | - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 |       |  |

| JSN        |                                         | 1 1 1 |  |

| C TALL     | 1 1 1 2 2                               | 1 1 1 |  |

18EE34

## Third Semester B.E. Degree Examination, June/July 2023 Analog Electronic Circuit

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

1 a. Define Q or Operating point

(02 Marks)

- b. What is a clipper circuit? Explain the working of a double ended clipper with a suitable diagram. (08 Marks)

- c. List various types of clamper circuit. With a neat circuit diagram, explain the working of a negative clamper. (10 Marks)

OR

- 2 a. Discuss emitter stablized bias circuit. Also derive expression for I<sub>B</sub>, I<sub>C</sub>, V<sub>B</sub> and V<sub>c</sub>. (10 Marks)

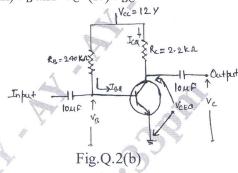

- b. Determine the following for the fixed bias configuration of Fig.2(b). Assume  $\beta$ =50.

- (i)  $I_{BQ}$  and  $I_{CQ}$  (ii)  $V_{CEQ}$  (iii)  $V_B$  and  $V_C$  (iv)  $V_{BC}$

(10 Marks)

## Module-2

- 3 a. Derive an expression for A<sub>y</sub> , Zi and Zo of CE voltage divider bias circuit using hybrid model. (10 Marks)

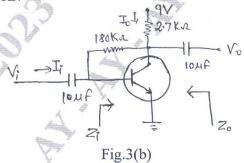

- b. For the collector feedback configuration of Fig 3(b), calculate (i)  $r_e$  (ii) Zi and Zo (iii)  $A_y$  and  $A_I$  Consider  $\beta$ =200,  $r_o$ =60Kr.

(10 Marks)

OR

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

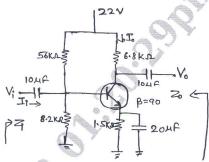

For the network of fig 4(a), determine: (i)  $r_e$  (ii)  $Z_i$  (iii)  $Z_o$  ( $r_o$ =00) (iv)  $A_v$  ( $r_o$ = $\infty$ ) a.

Fig.4(a)

Why hybrid model is called as hybrid? Obtain h – parameters from equivalent circuit of b. common – emitter configuration. (10 Marks)

Module-3

- 5 a. Define Multistage Amplifier. Derive voltage gain and current gain of a two stage cascaded amplifier. (10 Marks)

- b. Derive an expression for Zi and Ai for Darlington Emitter follower circuit. (10 Marks)

OR

a. Find out input and output impedance of a current series feedback amplifier. (10 Marks)

b. Determine the voltage gain, input and output impedance with feedback for voltage series

feedback having A=-100,  $Ri=10~k\Omega$ ,  $R_0=20~k\Omega$  for feedback of i)  $\beta=-0.1$  and ii)  $\beta=-0.5$ .

(10 Marks)

(10 Marks)

Module-4

- 7 a. With a neat circuit diagram, explain the AC Operation of series fed class A amplifier.

Also derive maximum efficiency of the amplifier. (10 Marks)

- b. Show that maximum efficiency of Class B push pull power amplifier is 78.54%. (10 Marks)

OR

- 8 a. Explain the working of R.C phase shift oscillator. If  $R=1~k\Omega$ ,  $R_c=1~k\Omega$  and  $C=0.1\mu f$ , Calculate the frequency of oscillations. (10 Marks)

- b. Discuss the working of Wein Bridge Oscillator, with a suitable diagram.

Module-5

- 9 a. Describe the working and characteristics of M Channel JFET. (10 Marks)

- b. For a self bias circuit,  $V_{DD}$  = + 20 ,  $R_D$  = 3.3 k $\Omega$  ,  $R_G$  = 1 M $\Omega$  ,  $R_S$  = 1 k $\Omega$  ,  $I_{DSS}$  = 8mA and  $V_P$  = -6V. Determine i)  $V_{GS}$  ii)  $I_D$  iii)  $V_{DS}$  iv)  $V_S$  v)  $V_G$  vi)  $V_D$ . (10 Marks)

OR

10 a. With a neat structure, explain the operation of an n – channel depletion type MOSFET.

(10 Marks)

b. Compare JFET with MOSFET. Sketch the transfer characteristics for an N- channel depletion type MOSFET with  $I_{DSS}=10 \text{mA}$  and  $V_P=-4V$ . (10 Marks)

\* \* \* \* \*