| USN |  |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|--|

10EE56

## Fifth Semester B.E. Degree Examination, Feb./Mar.2022 Linear IC's and Applications

Time: 3 hrs.

Max. Marks:100

Note: Answer any FIVE full questions, selecting at least TWO questions from each part.

## PART - A

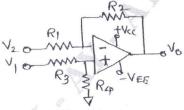

1 a. Analyse and name the circuit shown in Fig. Q1 (a). Assume that  $R_1 = R_2 = R_3 = R_4 = R$ . (05 Marks)

Fig. Q1 (a)

- b. Draw the circuit of High Input impedance capacitor coupled voltage follower and list the design steps. Also derive the expression for input impedance.. (08 Marks)

- c. A capacitor coupled non-inverting amplifier is to operate with +24 V supply. Voltage gain = 100 and output voltage  $V_0 = 5$  V. Lower cut off frequency  $f_1 = 75$  Hz and minimum load resistance  $R_L = 5.6$  K  $\Omega$ . Using a 741 op-amp design a suitable circuit.

(07 Marks)

- 2 a. Explain phase lag compensation network used for an op-amp circuit with reference to frequency response. (06 Marks)

- b. Calculate cut off frequency limited rise time for a voltage follower circuit using 741 op amp. Also determine slew rated limited rise time if output amplitude is 5 V. When op amp upper cut off frequency is 100 kHz, determine maximum output rise time and the maximum pulse amplitude at that rise time. (Assume SR = 0.5 V/μsec)..

- c. List precautions to be taken for op-amp circuit stability operation.

(06 Marks)

- 3 a. Explain a full wave precision Rectifier circuit using a summing circuit and a precision half wave rectifier. Show the waveforms. (08 Marks)

- b. A  $\pm$  5V 10 kHz square wave from a signal source with a resistance of 100  $\Omega$  is to have it's positive peak clamped precisely at ground level. Tilt on the output is not to exceed 1% of peak amplitude of the wave. Design a suitable op-amp circuit with supply of  $\pm$ 12V.

(06 Marks)

With a neat circuit, explain working of a sample and hold circuit.

(06 Marks)

- 4 a. Explain a capacitor coupled zero crossing detector circuit summarize design steps and show the waveforms. (06 Marks)

- b. Draw an inverting Schmitt Trigger circuit with different UTP and LTP. Explain its operation show the hysteresis characteristic and waveforms. (08 Marks)

- c. Draw an opamp based monostable circuit. Draw waveforms at various points. Write an expression for the output pulse width. Clearly mention various terms that appear in the expression.

(06 Marks)

PART - B

- Draw a triangular / rectangular waveform generator using op-amps. Explain the operation of 5 circuit. Also explain how frequency and duty cycle of output can be achieved. (09 Marks) (05 Marks)

- Compare a RC phase shift oscillator with a wein bridge oscillator. b.

- Design a RC phase shift oscillator with following specifications: frequency of output =  $3.5 \,\text{kHz}$ , supply voltage =  $\pm 12 \,\text{V}$ . (06 Marks)

- Compare a wide band pass filter with a narrow band pass filter. (05 Marks) 6

- Design a band pass filter using a single 741 op amp. The centre frequency is to be 1 kHz and pass band  $\pm 33 \,\mathrm{H}$  on either side of centre frequency.

- c. By means of block diagram, show the implementation of a band reject filter using, (i) High pass filter and low pass filter (ii) Band pass filter. Show the frequency response of Bond (07 Marks) reject filter.

- What is a Universal filter? Briefly outline the procedure for implementing a desired filter (08 Marks) function.

- With a neat circuit, explain operation of a phase locked loop based frequency multiplier b. (06 Marks) circuit.

- What is a switched capacitor filter? Explain how it can be used to simulate a resistor. (06 Marks)

- Define performance parameters of voltage regulator. (04 Marks) 8

- With a neat circuit, explain voltage follower type regulator. (08 Marks)

- c. For a voltage follower regulator designed with  $V_s = V_{CC} = 12 \text{ V}, \ V_O = 6.3 \text{V}, \ R_1 = 270 \ \Omega$  . The zener diode Z has  $V_Z = 6.3$  V and  $Z_Z = 7$   $\Omega$  with  $I_{Lmax} = 42$  mA. Source resistance is 25 Ω. Determine (i) Line regulation (ii) Load regulation (iii) Ripple rejection for the (08 Marks) circuit. Draw the circuit.