18ECS331

Third Semester M.Tech. Degree Examination, Jan./Feb. 2021

RF and Microwave Circuit Design

Time: 3 hrs.

WEALORE

Max. Marks: 100

Note: 1. Answer any FIVE full questions, choosing ONE full question from each module.

2. Use of Smith Chart is permitted

# Module-1

1 a. Write the reasons for using RF/microwaves.

(06 Marks)

b. Briefly explain the applications of RF/Microwave signal.

(08 Marks)

c. Explain Low RF design considerations and RF circuits design steps.

(06 Marks)

### OR

- 2 a. Design a circuit to match a  $100\Omega$  source to a  $1k\Omega$  load resistance at  $f_0 = 100 MHz$ . Assume that a DC voltage must also be transferred from the source to the load and all elements are perfect. (07 Marks)

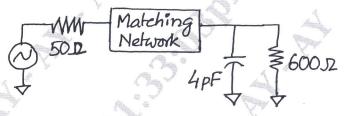

- b. Design a matching network that will match a source resistance of  $50\Omega$  to a capacitive load at  $f_0 = 75 \text{MHz}$ , as shown in Fig Q2(b). The matching circuit should block DC to the output. Use the resonance method

Fig Q2(b)

(08 Marks)

c. Explain unity property and zero property of [S] matrix.

(05 Marks)

### Module-2

a. Derive the mathematical expression for Smith Chart.

(08 Marks)

- b. Find the input impedance of a transmission line  $(z_0 = 50\Omega)$  that has a length of  $\lambda/8$  and is connected to a load impedance  $z_L = 50 + j50\Omega$ . (05 Marks)

- c. Write short note on circular and radial scales of Smith Chart.

(07 Marks)

## OR

4 a. Write the steps to determine the input impedance for a given load using Smith Chart.

(04 Marks)

b. What is Stub? Write the steps to determine input impedance using single series stub.

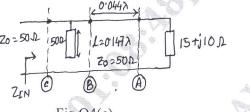

c. Consider a transmission line with  $z_0 = 50\Omega$  terminated in a load  $z_L = 15 + j10\Omega$  as shown in Fig Q4(c). Calculate the input impedance of the line, where the shut open stub is located a distance of d = 0.044 $\lambda$  from the load and has a length of  $\ell$  = 0.147 $\lambda$ .

(10 Marks)

# Module-3

Determine the stability of a GaAs FET that has the following S-parameters at 2 GHz in a  $50\Omega$  system both graphically and mathematically,

$S_{11} = 0.89 \angle -60^{\circ}, S_{21} = 3.1 \angle 123^{\circ}, S_{12} = 0.02 \angle 62^{\circ}, S_{22} = 0.78 \angle -27^{\circ}.$ (08 Marks)

- Define mismatch factor. Determine the relationship between input port VSWR and mismatch factor. (06 Marks)

- Write short note on Unilateral Figure of Merit. (06 Marks)

- Explain the following: 6

- i) Noise model of noisy resistor ii) Equivalent noise temperature (06 Marks)

- Show that  $F = F_1 + \frac{F_2 1}{G_{A1}}$ , for cascaded two stage network. (06 Marks)

- A wideband amplifier (2 4 GHz) has gain of 10dB, an output power of 10dBm and a noise figure of 4dB at room temperature. Find the noise power in dBm. (08 Marks)

# Module-4

- Write the steps for small signal amplifier RF/MW circuit design. (06 Marks)

- Write the design steps of Low Noise Amplifier design. (05 Marks)

- c. Design a high gain amplifier for a power gain of 15dB at a frequency of 3GHz, if the selected bipolar transistor has the following S parameters at  $V_{CE} = 4V$  and  $I_C = 5mA$ .

$$[S] = \begin{bmatrix} 0.7 \angle -155^{\circ} & 0\\ 4 \angle 180^{\circ} & 0.51 \angle -20^{\circ} \end{bmatrix}$$

(09 Marks)

### OR

Describe the mixer operation in down converter, up converter and harmonic mixer.

(06 Marks)

b. Consider a single - ended mixer having the following port VSWR values at 10GHz:  $(VSWR)_{RF} = 2.0$ ,  $(VSWR)_{IF} = 3.0$ ,  $L_h = 3dB$ . The diode used in the mixer has:

$R_j = 100\Omega$ ,  $R_s = 2\Omega$  and  $C_j = 0.2pF$ . What is the conversion loss of the mixer? (08 Marks)

Analyze the construction and working of a one Diode Mixer. (06 Marks)

## **Module-5**

- Write short notes on: i) Varactors ii) PIN Diodes. (10 Marks)

- Explain the loaded line phase shifter and derive the expression for transmission coefficient and Insertion loss for the same. Also briefly mention the disadvantages for loaded line phase shifter. (10 Marks)

## OR

- Give a detailed comparison between hybrid and monolithic MICS. 10 (10 Marks)

- Explain in details chip mathematics for RFIC. (10 Marks)