17EC34

# Third Semester B.E. Degree Examination, Jan./Feb. 2021 **Digital Electronics**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

# Module-1

- 1 Define the following:

- i) Combinational circuit

- ii) Sequential circuit

- iii) Canonical SOP

- Canonical POS iv)

- V) Prime Implicant

- Essential prime implicant. vi)

(08 Marks)

- Express the following equations into decimal notations:

- H = f(A, B, C) = A'BC + A'BC + ABCi)

- T = f(a, b, c) = (a + b' + c) (a + b' + c') (a' + b' + c)

(08 Marks)

Write mirror image version 5-variable K-map.

(04 Marks)

### OR

- 2 Obtain minimal expression using k-map for the following incompletely specified function  $F(a, b, c, d) = \sum m(0, 1, 4, 6, 7, 9, 15) + \sum d(3, 5, 11, 13)$  and draw circuit diagram using gates. (10 Marks)

- b. Simplify the following using Quine-Mcclusky method

$s = f(w, x, y, z) = \sum (1, 3, 13, 15) + \sum d(8, 9, 10, 11)$

(10 Marks)

## Module-2

- 3 Explain the analysis and design procedure for combinational circuit with example. (10 Marks)

- Implement full substractor using 3:8 decoder and write truth table. b.

(10 Marks)

Design full adder using i) 8:1 MUX ii) 4:1 MUX.

(10 Marks)

b. Design 4 to 16 decoder using 3 to 8 decoder. (05 Marks)

Explain look ahead carry adder and give its advantages and disadvantages.

(05 Marks)

### Module-3

- What is flipflop? Discuss working principle of SR flipflop with its TT and write 5 characteristics equations. (10 Marks)

- Sketch timing diagram for JK flipflop and D-flipflop. b.

(05 Marks)

Explain the operation of a switch debouncer built using SR-latch with the help of waveforms. (05 Marks)

OR

- Explain the working of a master-slave JK flip-flop with timing diagram. Show how race (10 Marks) around condition is eliminated. Explain setup time, hold time and propagation delay for timing considerations. (05 Marks)

- b. (05 Marks) Write characteristics equation for D and T flip-flop.

Module-4

- Explain with diagram, operation and waveforms Serial In Serial Out (SISO) shift left mode 7 (10 Marks) register. (10 Marks)

- Design BCD ripple counter using JK flip-flop. b.

Design an synchronous mod 5 counter using JK flip-flop and draw its timing diagram. 8 a. (10 Marks)

(05 Marks) Explain ring counter with timing sequence. **b**.

Write a note on Johnson counter.

(05 Marks)

Module-5

- Draw and explain the block diagram of Moore and Mealy model with example and also 9 (10 Marks) compare both.

- Define, present state, next state, state diagram state table and state assignment. (05 Marks) b.

- Draw and explain Moore JK-flipflop state diagram.

(05 Marks)

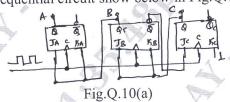

Analyze the synchronous sequential circuit show below in Fig.Q.10(a).

(12 Marks)

sequence counter using JK flipflops count synchronous to b. Design (08 Marks) 0, 1, 2, 4, 5, 6, 0, 1, 2. Use state diagram and state table.