## Third Semester B.E. Degree Examination, June/July 2019

## **Logic Design**

Time: 3 hrs.

Max. Marks:100

## Note: Answer any FIVE full questions.

- Verify the following Boolean manipulations and justify each step with respect to postulate 1 a. or theorem:

- i)  $abc + ab\overline{c} + a\overline{b}c + \overline{a}bc = ab + ac + bc$

(06 Marks) ii)  $(ab+c+d)(\overline{c}+d)(\overline{c}+d+e) = ab\overline{c}+d$

- Express the following Boolean functions by Maxterm canonical formula without first constructing the Truth-Table.  $f(x, y, z) = x + \overline{xz}(y + z)$ (04 Marks)

- Realize 4-bit odd Parity generator using X-OR gates only.

(10 Marks)

Using K-maps determine all minimal sums and minimal products for the following Boolean 2 a. functions. In each case indicate essential Prime Implicants.

(05 Marks)  $f(w, x, y, z) = \sum m(0, 1, 6, 7, 8, 14, 15)$ b. Design a combinational network whose input is a 4-bit binary number and whose output is a

2'S complement of input number.

c. For the following Boolean function, determine minimal sums and minimal products using VEM technique, where w, x and y are the map variables and z is map entered variable. (10 Marks)  $f = \sum m(2, 3, 5, 12, 14) + dc(0, 4, 8, 10, 11)$

Using the Quine-McCluskey method and prime implicant table reductions, determine the

minimal sums for the incomplete Boolean function.  $f(v, w, x, y, z) = \sum m(4, 5, 9, 11, 12, 14, 15, 27, 30) + dc(1, 17, 25, 26, 31)$

Explain the procedure for loading a K-map using map entered variable technique. Write the map entered variable K-map for the Boolean function.

$$f(w, x, y, z) = \sum m(2, 9, 10, 11, 13, 14, 15)$$

(10 Marks)

a. Explain the operation of a two input TTL NAND-gate with totem-pole output with a neat (08 Marks) circuit diagram.

b. What is a FET? Explain how to construct a resistor with the n-channel, enhancement type (06 Marks)

Explain with the help of a circuit diagram the operation of a two input CMOS nor-gate.

(06 Marks)

With a block diagram describe the principle of operation of a carry Look-ahead-adder. 5 (06 Marks)

What is a Programmable LOGIC Array (PLA)? Describe with a logic diagram the principle (08 Marks) of operation of a PLA. What are its advantages?

c. Implement the following Boolean function using 8:1 multiplexer.

$F(A,B,C,D) = \overline{A}B\overline{D} + ACD + \overline{B}CD + \overline{AC}D$

(06 Marks)

3

- 6 a. What is a sequential circuit? Discuss the different types of sequential circuits. (06 Marks)

- b. With a neat logic diagram and timing waveforms describe the operation of a master-slave JK flip-flop. (06 Marks)

- c. A stable assignment table for a mod-5 counter is given below:

| 5151111 |   |       |       |       |

|---------|---|-------|-------|-------|

|         | S | $Q_2$ | $Q_1$ | $Q_0$ |

|         | 0 | 0     | 0     | 0     |

|         | 1 | 0     | 0     | 1     |

|         | 2 | 0     | 1     | 1     |

|         | 3 | 1     | 1     | 1     |

|         | 4 | 1     | 1     | 0     |

|         |   |       |       |       |

Derive a counter configuration.

(08 Marks)

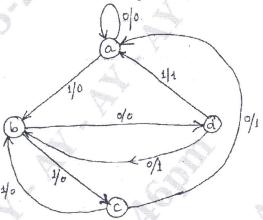

7 a. Design a clocked synchronous sequential machine using D-Flip Flops for the following [Fig.Q7(a)] state diagram. Use state reduction if possible. Also draw the logic diagram.

Fig.Q7(a)

(10 Marks)

- b. Design a synchronous Mod-6 counter using T-FF. Write state table and reduce the expression using K-map. Draw the logic diagram. (10 Marks)

- 8 Write short notes on:

- a. Implies and subsumes

- b. Fan-in and Fan-out

- c. Universal shift register

- d. Programmable logic arrays

(20 Marks)

\* \* \* \* \*