## Sixth Semester B.E. Degree Examination, June/July 2018 Microelectronics

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

- a. Derive the expression for drain to source current for triode and saturation regions of n-MOSFET. (10 Marks)

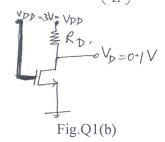

- b. Design the circuit shown in Fig.Q1(b) to obtain a drain voltage of 0.1V. Find the value of  $R_D$ . At the operating point, let  $V_t = 0.5V$  and  $K'_D \left( \frac{W}{V} \right) = 2mA/V^2$ . (06 Marks)

OR

- 2 a. Derive the expression for drain current under channel length modulation (08 Marks)

- b. What is body effect? Write the expressions for V<sub>t</sub> related to body effect and draw its small signal model. (04 Marks)

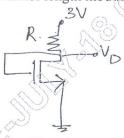

- c. Design the circuit in Fig.Q2(c) to obtain  $I_D=80~\mu A$ , find the value required for R and find the DC voltage  $V_D$ . Let the NMOS transistor have  $V_t=0.6V$ ,  $\mu_n cox=200~\mu A/V^2$ ,  $L=0.8\mu m$  and  $W=4~\mu m$ . Neglect channel length modulation. (04 Marks)

Fig.Q2(c)

## Module-2

- 3 a. Briefly explain any two types of baising methods in MOS amplifier circuits. (06 Marks)

- b. Derive the expression for transconductance gm and voltage gain Av for a CS amplifier with small input signal (10 Marks)

## OR

- 4 a. Develop a Tequivalent model for the MOSFET from a hybrid  $\pi$  model. (08 Marks

- b. For a n-channel MOSFET with  $t_{ox}=10$ nm, L=1.0 µm, W=10 µm,  $L_{OV}=0.05$  µm,  $C_{sbo}=C_{dbo}=10$  fF,  $V_0=0.6$  V,  $V_{SB}=1$  V and  $V_{DD}=2$  V. Calculate the following capacitances when the transistor is operating in saturation  $C_{OX}$ ,  $C_{OV}$ ,  $C_{gs}$ ,  $C_{gd}$ ,  $C_{db}$ ,  $C_{sb}$ . Given  $E_{OX}=3.45\times10^{-11}$  F/m<sup>2</sup>. (08 Marks)

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

Module-3

- Make a comparison between BJT and MOSFET (Any 4 characteristics). (08 Marks)

- Determine the G<sub>V</sub>, A<sub>y</sub>, R<sub>out</sub>, R<sub>in</sub>, A<sub>VO</sub> for a common source MOS amplifier without source (08 Marks) degeneration.

OR

- Explain the operation of a MOS current steering circuit and mention its advantage. (08 Marks)

- Consider CG amplifier designed using a circuit. Given  $g_m = 1 \text{mA/V}$  and  $R_D = 15 \text{ k}\Omega$ . Find  $R_{in}$ ,  $R_{out}$ ,  $A_V$ ,  $A_{VO}$ , and  $G_V$  for  $R_L = 15k\Omega$  and  $R_{sig} = 50\Omega$ . (08 Marks)

Module-4

- a. A CMOS CS amplifier fabricated in 0.18 $\mu$ m technology has W/L = 7.2 $\mu$ m/0.36 $\mu$ m for all transistor  $K_n' = 387 \mu A/V^2$ ,  $K_P' = 86 \mu A/V^2$ ,  $I_{ref} = 100 \mu A$ ,  $V_{An}' = 5 V/\mu m$  and  $|V_{AP}| = 6 V/\mu m$ . Find  $g_{m_1}$ ,  $r_{0_1}$ ,  $r_{0_2}$  and voltage gain.

- For a CG amplifier with active load determine the expression for R<sub>i</sub>, A<sub>VO</sub>, A<sub>V</sub>, G<sub>VO</sub>, G<sub>V</sub>, R<sub>O</sub>.

OR

- Write a notes on: i) Double cascode ii) Folded cascode. (08 Marks)

- b. Explain CMOS implementation of common source amplifier. (08 Marks)

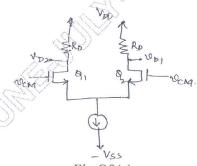

- For a MOS differential pair with a common mode voltage V<sub>CM</sub> is shown in Fig. Q9 (a). Let  $V_{DD} = V_{SS} = 1.5V$ ,  $K'_{n} \left(\frac{W}{L}\right) = 4mA/V^{2}$ ,  $V_{t} = 0.5V$ , I = 0.4 mA and  $R_{D} = 2.5k\Omega$ . Neglect

- channel length modulation. i) Find V<sub>OV</sub> and V<sub>GS</sub> for each transistor

- ii) For  $V_{CM} = 0$ , find  $V_S$ , id, id<sub>2</sub>,  $Vd_1$  and  $Vd_2$

- iii) Repeat (b) for  $V_{CM} = +1V$

- iv) What is the highest value for which Q<sub>1</sub> and Q<sub>2</sub> are in saturation? If current I requires a minimum voltage of 0.4V to operate properly. What is the lowest allowed V<sub>S</sub> and hence V<sub>CM</sub>? (10 Marks)

Fig.Q9(a)

What is the effect of mismatch of R<sub>D</sub> on CMRR of a MOS differential amplifier? (06 Marks)

OR

10 a. Explain the operation of MOS differential pair with a differential input signal.

Explain 2-stage CMOS OPAMP configuration.

(08 Marks) (08 Marks)