## CBCS Scheme

USN

15EE34

# Third Semester B.E. Degree Examination, Dec.2017/Jan.2018 Analog Electronics Circuits

Time: 3 hrs.

Max. Marks: 80

Note: Answer FIVE full questions, choosing one full question from each module.

Module-1

- a. Explain the different biasing circuits of BJT, for each circuit find an expression for stability factor. Also describe how to find the Q point of the circuit. (09 Marks)

- b. Draw the circuit of voltage divider bias. Take the circuit parameters as,  $V_{CC}=10~V$ ,  $R_2=17~K\Omega$ ,  $R_1=83~K\Omega$ ,  $R_C=2~K\Omega$ ,  $R_E=0.5~K\Omega$ , find Q point and terminal voltages. The transistor has  $\beta=100$  and  $V_{BE}=0.7~V$ . (07 Marks)

OR

- 2 a. Explain the operation of transistor as a switch with the help of neat circuit diagram and waveforms. Also enumerate the design procedure. (08 Marks)

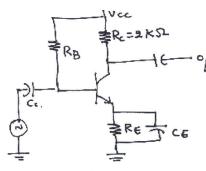

- b. For the following circuit, find the Q point,

Take  $V_{CC}$  = 10 V,  $R_{C}$  = 1 K $\Omega$ ,  $R_{E}$  = 0.5 K $\Omega$ ,  $\beta$  = 50,  $V_{BE}$  = 0.7 V

Module-2

- a. Draw the circuit of emitter follower with voltage divider biasing and derive expressions for current gain, voltage gain input and output impedances. (08 Marks)

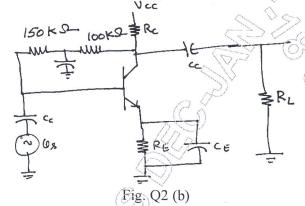

- b. For the following circuit find current gain, voltage gain, input and output impedances.

(08 Marks)

Fig. Q3 (b)

#### OR

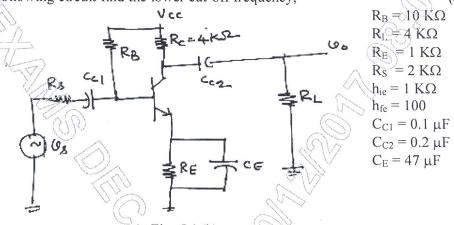

With neat diagrams derive expressions for Miller capacitances (C<sub>MI</sub> and C<sub>MO</sub>) For the following circuit find the lower cut-off frequency, (08 Marks)

Fig. Q4 (b) Module-3

- 5 Two amplifiers are cascaded. The load resistance  $R_L = 20 \text{ K}\Omega$  and internal resistance of the voltage source is 2 K $\Omega$ . Find the

- Loaded voltage gain of each stage.

- (ii) Total voltage gain of cascaded amplifier with Rs.

- Current gain of cascaded amplifiers (iii)

- (iv) Output impedance.

The first stage bias No load voltage gain = 1, Input impedance = 500 K $\Omega$ ,

Output impedance = 1 K, The second stage has a no load voltage gain of 300, input impedance of 1 K $\Omega$  and output impedance of 50 K $\Omega$ (08 Marks)

With neat diagrams explain cascade amplifier.

(08 Marks)

#### OR

- Derive suitable expression to explain the effect of negative feedback on, (i) Gain stability (ii) Distortion in amplifier.

- The open loop gain of an amplifier is subjected to variation of ±10% due to changes in temperature. Using such an amplifier design a feedback amplifier such that the closed loop gain of the amplifier is  $150\pm1\%$ . Find the value of open loop gain of the amplifier and feedback factor. (08 Marks)

### Module-4

Draw the circuit of class-A transformed amplifier and explain its operation. Derive an expression for maximum efficiency of conversion with the help of neat waveforms.

b. A transistor amplifier has zero signal collector current of 40 mA. When an a consource is connected, the dc collector current is 50 mA. The peak fundamental current in collector is

30 mA. Find second harmonic distortion and output ac power. (08 Marks)

#### OR

- Draw the circuit of Wien bridge oscillator and explain its operation. Also derive an expression for frequency of oscillation.

- b. Explain with neat circuit diagram, the operation of crystal oscillator and write the expression for frequency of oscillation. (06 Marks)

Module-5

- 9 a. With neat diagrams, explain the construction, working and static characteristics of n-channel JRET. (08 Marks)

- b. Draw the circuit of common source amplifier with bypass capacitor and derive an expression for voltage gain and output impedance. (08 Marks)

OR

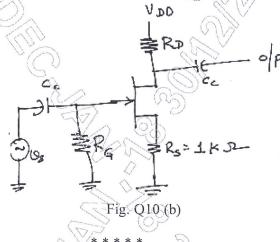

- 10 a. With the help of neat diagrams, explain the construction, working and characteristics of n-channel depletion MOSFET. (08 Marks)

- b. A common source amplifier without bypass capacitor has  $R_D = 2 \, K\Omega$ ,  $R_S = 1 \, K\Omega$ ,  $R_G = 1 \, M\Omega$ , find voltage gain and output impedance  $g_m = 2 \, m \, O$ . (08 Marks)